SiTime製品パッケージ

|

振荡器类型/包装面积(mm x mm)

|

|||||||||

|---|---|---|---|---|---|---|---|---|---|

| QFN 7.0 x5.0 |

QFN 5.0 x3.2 |

QFN 3.5 x3.0 |

QFN 3.2 x2.5 |

QFN 2.5 x2.0 |

QFN 2.0 x1.6 |

SOT23-5 2.9 x2.8 |

DFN 2.0 x1.2 |

CSP 1.5 x0.8 |

|

|

シングルエンド発振器 |

|

|

|

|

|

||||

|

シングルエンドXT (极薄)発振器 |

|

||||||||

|

32 kHz発振器 |

|

|

|||||||

|

差動発振器 |

|

|

|

||||||

|

betway手机客户端

|

|

||||||||

水晶製品からの置き換え

SiTimeは,水晶振動子と水晶発振器から100%置き換え可能な業界標準パッケージを提供します。これらのSiTime製品は水晶製品とピン互換があり,一般的な水晶発振器のPCBレイアウトに収まるため,基板設計を変更することなく水晶製品からSiTime製品へ置き換えが可能です。

実装上の信頼性

SiTimeは,はんだ接合における信頼性を重視するアプリケーション向けに58必威 を提供します。これらはリードの付いたパッケージで,よりコスト競争力のある製品です。またX線不使用によるはんだ接合部の検査と,より簡単な再加工が可能です。

超小型パッケージ

とても小さいスペースを要求するアプリケーションには,SiTimeの超小型32 khz発振器製品(1.5×0.8×0.6毫米,CSP(チップ•スケール•パッケージ))を推奨します。これらは世界最小の発振器であり,CSPパッケージ技術を利用した最初の製品です。

低プロファイルパッケージ

SiTimeのMEMS振動子は非常に小さく,それを使う発振器も水晶製品より薄く製造可能です。フットプリントサイズによって異なりますが,標準パッケージは厚さ0.75 ~ 0.90毫米です。また3.5 x3.0mmのXTパッケージはたった0.25毫米(紙3枚分)の厚さであり,世界で最も薄い精密発振器です。

プラスチックパッケージ

SiTimeのMEMS振動子とCMOSは,プラスチックパッケージにモールドされます。SiTimeは低コストのプラスチック射出成形状パッケージを使用しています。これは,より高い信頼性,より低いリード・インダクタンスと熱性能向上を実現するためです。SiTime製品はすべて100% rohsに準拠しており,鉛フリーです。そして,乾燥などの環境条件を気にする必要もありません火星科学实验室(((水分敏感性级别)1)。

また,水晶デバイスメーカーはセラミックまたは金属パッケージを使用しており,それらは高価であると共に,供給元が限られサプライチェーンの問題を起こしかねません。それに対し,SiTimeはエレクトロニクス業界で幅広く使用されていて,多くのサプライヤーから入手可能な,業界標準のプラスチックパッケージを使用しています。

業界標準半導体製造プロセス

MEMSベースのタイミングデバイスは,標準的な半導体パッケージ工程に従い,パッケージされます。さらに最先端の半導体パッケージング技術が使用可能です。SiTimeのシリコンMEMS振動子を製造するEpi-Sealプロセスは、高温のエピタキシャル工程で振動子やその周りの真空キャビティを綺麗にし、ベントを埋めます。個々の振動子を微小真空キャビティ内に封止することで、異物の排除や、信頼性の向上に繋がります。

MEMSベースのタイミングデバイスは,標準的な半導体パッケージ工程に従い,パッケージされます。さらに最先端の半導体パッケージング技術が使用可能です。SiTimeのシリコンMEMS振動子を製造するEpi-Sealプロセスは、高温のエピタキシャル工程で振動子やその周りの真空キャビティを綺麗にし、ベントを埋めます。個々の振動子を微小真空キャビティ内に封止することで、異物の排除や、信頼性の向上に繋がります。

SiTimeのMHz発振器は下記のパッケージ工程図のとおり,QFN(扁平无铅)パッケージに封止します。ダイシング後,MEMS振動子とCMOSは一般的な積層法を使い,フリップチップ実装や標準的なダイアタッチによって,リードフレーム・ストリップ,または基板実装されます。次に,MEMSとCMOSは細い金線や銅線でワイヤボンディングされ,密度の高いリードフレームや基板にトランスファーモールドされます。モールドされたデバイスは一体となり,最終的にテスト装置による標準的なテスト(手動または自動)が行われます。

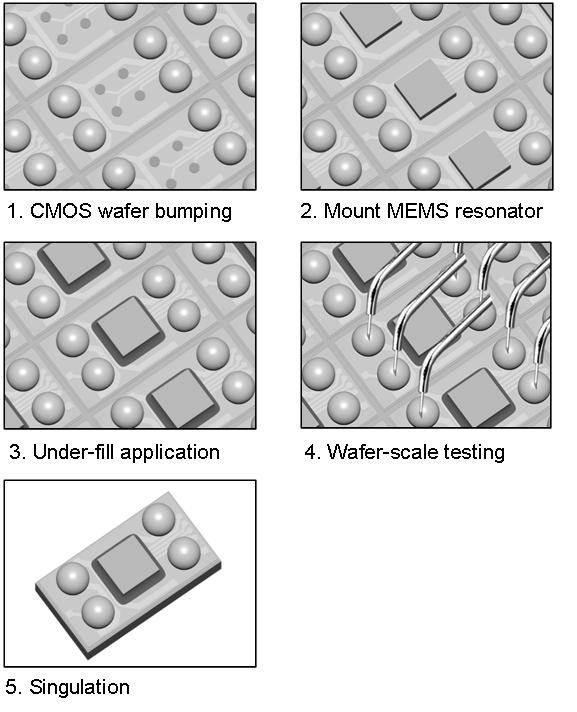

超小型発振器製品のパッケージ工程

次にWLCSP(晶圆级芯片尺寸包)の超小型μ权力発振器製品のパッケージ工程を紹介します。CMOSウェハーは,通常のCSPパッケージの組み立てラインでバンプ(突起状の接続電極)を作ります。そして,カットしたMEMSダイをCMOSウェハーにフリップチップ実装し,アンダーフィル材(エポキシ)で封止します。次に,このWLCSPウェハーを標準的な自動試験装置を用いてウェハースケールでテストした後に,ダイシングしてテープやリールで梱包します。

次にWLCSP(晶圆级芯片尺寸包)の超小型μ权力発振器製品のパッケージ工程を紹介します。CMOSウェハーは,通常のCSPパッケージの組み立てラインでバンプ(突起状の接続電極)を作ります。そして,カットしたMEMSダイをCMOSウェハーにフリップチップ実装し,アンダーフィル材(エポキシ)で封止します。次に,このWLCSPウェハーを標準的な自動試験装置を用いてウェハースケールでテストした後に,ダイシングしてテープやリールで梱包します。